| Printed Pages: 7                                                    |  | 1258    | EC-101 |

|---------------------------------------------------------------------|--|---------|--------|

| (Following Paper ID and Roll No. to be filled in your  Answer Book) |  |         |        |

| Paper ID : 131111                                                   |  | Roll No |        |

#### B.TECH.

# (SEM. I) THEORY EXAMINATION, 2015-16 ELECTRONICS ENGINEERING

[Time:3 hours]

[Total Marks:100]

Note: All sections are *compulsory*.

#### **SECTION-A**

- 1. Attempt **all** parts . All parts carry equal marks. Write answer of all part in short . (2x10-20)

- (a) What is the purpose of Delay block in CRO?

- (b) Define slew rate of an OPAMP.

- (c) Why Si is preferred over Ge for manufacturing of electronic devices.

- (d) In JFET  $I_{DSS}=6mA$ ,  $V_p=-3V$  biased at  $V_{GS}=-2V$ . Determine the value of  $g_m$ ?

- (e) Define Op-Amp and Draw its block diagram.

- (f) Explain Common Collector configuration in case of NPN transistor.

- (g) Explain ohmic region of the JFET.

- (h) What do you understand by 'cut-in' voltage of a diode?

- (i) Differentiate between deterministic and random signals.

- (j) Define need of unity gain amplifier using an OpAmp.

### **SECTION-B**

Attempt any five questions from this section. (10x5=50)

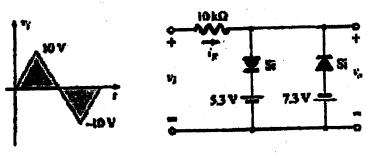

2. (i) Determin  $V_0$ , and draw the output waveform of the given network of Figure 1.

Figure 1

(ii) For the network of Figure 2, determine the range of V<sub>1</sub> that will maintain V<sub>1</sub> at 20 V without exceeding the maximum current rating of 60 mA.

Figure 2

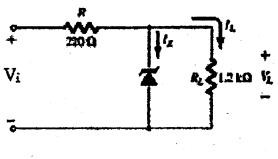

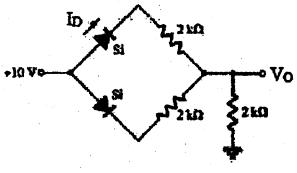

3. (i) Determine  $V_o$  and  $I_D$  for the network of Figure 3.

Figure 3

(2)

**EC-101**

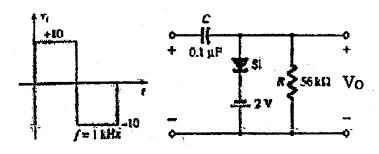

(ii) Sketch V<sub>o</sub> for the network of Figure 4 for the input shown.

Figure 4

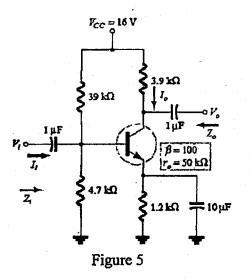

4. For the voltage divider configuration of Figure 5 determine  $r_0, A_0, Z_{in}$  and  $Z_0$ .

(4)

EC-101

- 5. Explain the following with the help of necessay diagrams using an Op-Amp.

- (i) Adder

- (ii) Integrator

- 6. (i) Enumerate with the help of a block diagram, of various elements involved in Digital Multimeter to measure the various range of Voltage and Current.

- (ii) Explain Differential amplifier in two mode of operation.

- 7. (i) Determine the output voltage of an op-amp for input voltages of  $Vi_1=100V$  and  $Vi_2=120V$ . The amplifier has a differential gain of  $A_d=4000$  and the value of CMRR is:

- (a) 150 (b)  $10^3$

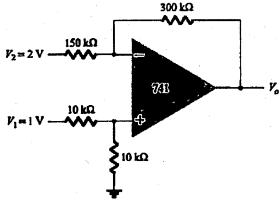

- (ii) Find V<sub>0</sub> for the circuit shown in Figure 6

Figure 6

- 8. With the help of a neat block diagram, explain the working of a CRO and describe the method of measurement of phase and frequency using CRO.

- 9. Explain with the help of a neat diagram working and characteristic curve of Ramp type digital voltmeter.

## **SECTION-C**

Attempt any two questions from this section. (15x2=30)

- 10. (i) Explain the working and characteristic of Tunnel diode with the help of a neat diagram.

- (ii) Describe with the help of circuit diagram, working of a voltage multiplier.

- 11. (i) Explain construction working and characteristics of P-channel Enhacement type MOSFET.

- (ii) Draw and explain the input and output characteristics.

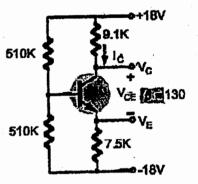

12. (i) For the common collector configuration in Figure 7, determine  $I_B$ ,  $I_C$ ,  $V_E$ ,  $V_{CE}$ .

Figure 7

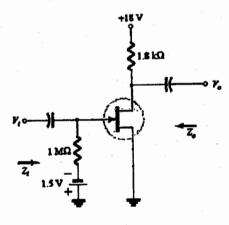

(ii) Determine  $Z_1$ ,  $Z_0$  and Av for the circuit of Figure 8. if  $I_{DSS}=12\text{mA}$ ,  $V_p=-6\text{V}$ , and Yo=40 microSiemen.

Figure 8

1800

(7) —x—